سوپراسکالر

'این پروسسورها همزمان بیش از یک دستورالعمل را اجرا میکنند؛ به عبارت دیگر پایپ لاین دستوری در این پروسسور به بهترین شکل ممکن استفاده میشود. که نمونه ایی از سوپر اسکالر درجه ۳ را در شکل زیر میبینیم

| دستور اول | OF۱ | D۱ | OPRF۱ | EXE۱ | ST۱ | ||

| دستور دوم | OF۱ | D۲ | OPRF۲ | EXE۲ | ST۲ | ||

| دستور سوم | OF۱ | D۳ | OPRF۳ | EXE۳ | ST۳ | ||

| دستور چهارم | OF۱ | D۱ | OPRF۱ | EXE۱ | ST۱ | ||

| دستور پنجم | OF۱ | D۲ | OPRF۲ | EXE۲ | ST۲ | ||

| دستور ششم | OF۱ | D۳ | OPRF۳ | EXE۳ | ST۳ | ||

| دستور هفتم | OF۱ | D۱ | OPRF۱ | EXE۱ | ST۱ | ||

| دستور هشتم | OF۱ | D۲ | OPRF۲ | EXE۲ | ST۲ | ||

| دستور نهم | OF۱ | D۳ | OPRF۳ | EXE۳ | ST۳ |

- معماری سوپراسکالر یک فرم از موازیسازی را به نام "موازیسازی در سطح دستور" با یک تک پردازنده پیادهسازی میکند.

موازیسازی در سطح دستور با استفاده از چندین پایپ لاین مستقل تأمین میشود، در واقع هر بار چند دستور(در شکل فوق ۳ دستور) به صورت موازی پردازش میشوند. از این رو اجازه میدهند توان عملیاتی سریع تر از دیگر حالات ممکن در یک کلاک باشد.

-یک پردازشگر سوپراسکالر با توزیع همزمان دستورالعملهای متفاوت به واحدهای عملیاتی اضافی (redundant)، پردازش بیش از یک دستورالعمل را انجام میدهد. هر واحد عملیاتی یک هسته جداگانه ندارد ولی یک منبع اجرایی جداگانه مانند ALU، شیفت دهنده بیتی یا یک ضربکننده را دارد.

-در طبقهبندی فلین(Flynn) یک پردازشگر سوپر اسکالر به عنوان یک پردازشگر MIMD طبقهبندی شدهاست.(دستورالعمل چندگانه، داده چندگانه)

-در حالی که CPU سوپراسکالر بهطور معمول پایپ لاین هم است ولی معماری پایپ لاین و سوپر اسکالر تکنیکهای متفاوتی برای افزایش کارایی دارند. که تکنیکهای سوپر اسکالر معمولاً شامل مشخصههای زیر است.

- دستورالعملها از یک جریان ترتیبی دستوری ناشی میشوند.

- وابستگی بین دستورالعملها به صورت سخت افزاری در زمان اجرا(run time)دائماً چک میشود.

- CPU چندین دستورالعمل را در یک سیکل کلاک می پذیرد

تاریخچه سوپراسکالر

CDC ۶۶۰۰های Seymour Cray از سال ۱۹۶۵ اغلب به عنوان اولین طرح سوپر اسکالر مورد توجه قرار گرفند.

ریز پردازندههای (Intel i۹۶۰ CA (۱۹۸۸و سریهای AMD ۲۹۰۰۰، ۲۹۰۵۰ نخستین ریز پردازندههای سوپر اسکالر تک تراشه ایی(single chip) تجاری بودند. CPUهای RISK مانند اینها نخستین ریز پردازندههایی بودند که از ایده سوپر اسکالر استفاده کرد، برای اینکه طرح RISK منجر به یک هسته ساده (simple core) گردد. بنابراین اجازه در برگرفتن واحدهای چند عملکردی (مانند ALUها) بر یک CPU در طراحی محدود به قواعد زمانی را میدهد.(این پاسخ پرسشی بود که چرا طرحهای RISK در دههٔ ۱۹۸۰ و ۱۹۹۰ از طرحهای CISC سریع تر بودند.)

به استثنای CPUهایی که در کاربرد کم مصرف قرار میگرفتند و سیستمهای جاسازی شده (embedded systems) و دستگاههای باتری (Battery-powered) اساساً تمامی CPUهای همه منظوره که از حدود سال ۱۹۸۸ توسعه یافت همگی سوپر اسکالر بودند.

P۵ Pentium نخستین پردازشگر سوپر اسکالر X۸۶ بود. Nx۵۸۶، P۶ Pentium Pro و AMD K۵ جزو اولین طرحهایی بودند که دستورهای آسنکرون X۸۶ را به صورت dynamic microcode (مانند سریهای قبلی micro-op) برای اجرای واقعی بر یک micro architecture سوپر اسکالر، رمز گشایی(decode) میکردند. این امر راه را برای زمان بندی دینامیک بافر شدن بخشی از دستورها باز نمود. و موارد موازیسازی بیشتری را در مقایسه با متدهای صلبی که در P۵ Pentium مورد استفاده قرار میگرفت قادر ساخت تا استخراج (extract) شوند. ضمناً مسئله speculative execution را ساده ساخت و موجب بالاتر رفتن فرکانس کلاک در مقایسه با طرحهایی چون Cyrix ۶x۸۶ گردید.

از اسکالر به سوپراسکالر

سادهترین پردازشگرها، اسکالر پردازشگرها (scalar processor) میباشند. هر دستورالعملی با یک پردازشگر اسکالر اجرا میشود نوعاً یک یا دو آیتم اطلاعات را در یک زمان اداره میکند. در مقابل هر دستورالعملی که به وسیله یک پردازشگر برداری (Vector processor) اجرا میشود در یک زمان بر روی تعداد زیادی آیتم اطلاعاتی کار میکند. یک پردازشکر سوپر اسکالر از یک ترکیب چندتایی، مرتب شدهاست.

هر دستورالعمل یک آیتم اطلاعاتی را پردازش میکند. اما واحدهای چند عملکردی اضافی با هر CPU وجود دارد. از این رو چندین دستورالعمل میتوانند آیتمهای اطلاعاتی جداگانه ایی را همزمان پردازش کنند.

طرح CPU سوپر اسکالر بر افزایش دقت توزیع دستورالعملها تأکید دارد و همچنین اجازه میدهد تا واحدهای چند عملکردی در هر زمانی قابل استفاده باشند. این امر بهطور فزاینده ایی از زمانی که تعداد واحد ها(Units) زیاد شده، مهم شدهاست. در هنگامی که CPUهای سوپر اسکالر

اولیه تنها دو ALU و یک FPU داشتند، یک طرح مدرن مانند PowerPC ۹۷۰ شامل چهار ALU، دو FPU و دو واحد SIMD بود. هنگامیکه توزیعکننده واحدها را با دستورالعملها تغذیه میکند اگر با مشکل روبه رو شود، عملکرد سیستم صدمه خواهد دید.

یک پردازشگر سوپر اسکالر معمولاً اجرای یک دستورالعمل اضافی را متحمل میشود اما فقط پردازش چندین دستورالعمل به صورت همزمان، یک معماری سوپر اسکالر را نمیسازد تا زمانی که، معماریهای پایپ لاین، چند پردازندگی یا چند هسته ایی، آن را بدست بیاورند اما با یک متد متفاوت.

در یک CPU سوپر اسکالر پخشکننده، دستور العملها را از روی حافظه می خواند و تصمیم میگیرد که کدامیک میتوانند به صورت موازی انجام گیرند، سپس آنها را به واحدهای عملیاتی اضافی که در کنار CPUهای منفرد هستند می فرستند. علاوه براین، پردازشگرهای سوپر اسکالر توانایی پیش بینی چندین پایپ لاین موازی را که هر یک از دستورالعملهای پردازشی آن، از یک نخ (Thread) مجزا باشد، داراست .

محدودیتها

بالا بردن کارایی که از طریق تکنیکهای سوپر اسکالر بدست میآید به ۳ چیز محدود میشود:

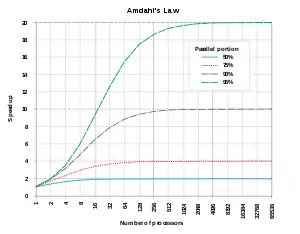

- درجه ذاتی موازیسازی در جریان دستورالعمل ها. به سطح موازیسازی دستورالعملها محدود میشود.

- پیچیدگی و زمان صرف شده ایی که توزیعکننده برای چک کردن وابستگیها دارد.

- انشعابهای دستورالعمل در حال پردازش

برنامههای باینری قابل اجرایی وجود دارند که درجه ذاتی موازیسازی آنها با هم متفاوت است. در بعضی موارد دستورالعملها به یک دیگر وابسته نمیباشند و میتوانند بهطور همزمان اجرا شوند. در موارد دیگر آنها وابستگی داخلی دارند: اثرات یک دستورالعمل در منابع یا نتیجه آن در دیگر منابع. دستورالعملهای ;a = b + c;، d = e + f میتوانند موازی با هم اجرا شوند و هیچکدام از نتایج وابسته به محاسبهٔ دیگری نیست. اما دستورالعملهای ;a = b + c;، b = e + f ممکن است بهطور موازی قابل اجرا نباشند.

وقتی که تعداد دستورالعملهای موازی افزایش پیدا میکند. هزینه چک کردن وابستگی به سرعت افزایش می یابد، و این موضوع با نیاز به چک کردن وابستگی در زمان اجرا و در کلاک CPU، تشدید میشود. این هزینهها شامل گیتهای منطقی اضافی مورد نیاز برای چک کردن و زمان تاخیری که به خاطر این گیتها به وجو میآید میباشد. تحقیقات نشان میدهد که تعداد گیتها در بعضی موارد به گیت و تأخیر نیز به رسیدهاست که تعداد دستورالعملهایی است که جزو دستور العملهای پردازشی میباشند و تعداد دستورالعملهایی که به صورت همزمان توزیع شدهاند.

اگر چه جریان دستورالعملها ممکن است شامل هیچ وابستگی داخلی نباشد، با این حال یک CPU سوپر اسکالر باید این موضوع را چک کند زیرا هیچ تضمینی وجود ندارد. یا بهطور دیگر در تشخیص یک وابستگی، خطا حاصل شود، نتایج غیر صحیح میباشد.

در این جا یک محدودیت عملی روی تعداد دستورالعملهایی که به صورت موازی قابل توزیع هستند داریم. در حالی که روند پیشرفت اجازه خواهد داد واحدهای عملیاتی را بیشتر کنیم، باری که از چک کردن وابستگی دستورالعمل هاست به سرعت زیاد میشود، که سوپر اسکالر دست یافتنی را به ۵ با ۶ دستورالعملهایی که بهطور همزمان توزیع شوند محدود میکند.

مباحث مرتبط

در مجموع این محدودیتها تحقیق را به سمت تغییرات دیگر معماریها مانند VLIW، EPIC، SMT و همچنین چند نخی و پردازش چند هسته ایی سوق میدهد.

با VLIW وظیفه سنگین چک کردن وابستگی، در زمان اجرا به وسیله سخت افزار برداشته شده و به کامپایلر محول میگردد.EPIC همانند VLIW است، با حافظهٔ نهان اضافی برای پیش واکشی دستورالعملها

چند نخی همزمان با نام اختصاری SMT، تکنیکی است جهت ارتقای بازده کلی CPUهای سوپر اسکالر. SMT به نخهای مستقل چندگانه اجرایی این امکان را میدهد تا بهتر مورد استفاده منابع تولید شده توسط معماریهای مدرن پردازشگرها قرار گیرند.

سوپر اسکالر با پردازشگرهای چند هسته ایی که واحدهای عملیاتی اضافی در تمام پردازشگرهای نیستند متفاوت است. یک تک پردازنده محاسبات خود را به وسیله واحدهای عملیاتی مانند ALU و شیفت دهنده و ضربکننده و ممیز شناور و غیره انجام میدهد. ممکن است نسخههای چندگانه ایی از هر واحد عملیاتی وجود داشته باشد که اجرای تعداد زیادی دستورالعمل را بهطور موازی ممکن سازد. که این با پردازشگرهای چند هسته ایی که همزمان دستورالعملها را از چند نخی (هر نخ برای یک هسته)گرفته و پردازش میکند متفاوت است و همچنین این با CPUهای پایپ لاین، که دستورالعملهای چندگانه میتوانند همزمان در مراحل مختلف اجرا باشند نیز تفاوت دارد.

تکنیکهای پیشنهادی متنوع صرفاً انحصاری نیستند. آنها میتوانند در یک تک پردازنده با هم ترکیب شوند. بنابراین یک CPU چند هسته ایی جایی که هر هسته، یک پردازشگر مستقل شامل موازیسازی پایپ لاین که هر پایپ لاین سوپر اسکالر باشد، محتمل وامری شدنی است و همچنین تعداد زیادی از پردازندهها هم دارای قابلیت برداری (Vector) باشد.

منابع

مشارکتکنندگان ویکیپدیا. «Superscalar». در دانشنامهٔ ویکیپدیای انگلیسی، بازبینیشده در ۲۰۱۱.