فلیپفلاپ

در الکترونیک دیجیتال فلیپفلاپ (به انگلیسی: Flip-flop) یا لچ (به انگلیسی: latch) نوعی مدار است که داری دو حالت پایدار است و میتواند ۱ بیت (که شامل حالت فلیپفلاپ است) را در خود ذخیره کند.یک فلیپفلاپ یک مدار نوسان ساز بای-استابل است. مدار میتواند به شکلی ساخته شده باشد، که به وسیله سیگنالهای گرفته شده از یک یا چند ورودی، یک یا چند خروجی را تولید کند. یک فلیپفلاپ یکی از حافظههای ابتدایی در مدارهای ترتیبی میباشد. فلیپفلاپها از بلاکهای اصلی مدارهای دیجیتال هستند و استفادههای فراوانی در رایانه و طراحی مدارهای مخابراتی دارند.

از فلیپفلاپهای برای طراحی سلولهای حافظه استفاده میشود. یک فلیپفلاپ امکان ذخیرهسازی یک بیت را دارد، که میتواند در حالت یک یا صفر باشد. چنین سلول حافظه ای برای نگهداری حالت، و مدارهایی که در الکترونیک به عنوان مدارهای ترتیبی یاد میشود، استفاده میشود. زمانی که از یک ماشین حالات متناهی استفاده میشود، خروجی نه تنها وابسته به ورودی فعلی است، بلکه وابسته به حالت موجود فعلی نیز میباشد(بنابراین وابسته به ورودی قبلی هم هست). همچنین میتوان برای شمارش واحد زمانی، همگاه سازی چند ورودی در زمانهای مختلف برای ساخت یک واحد زمانی جداگانه، استفاده کرد.

فلیپفلاپ میتواند به شکل ساده(شفاف یا غیر شفاف) یا همراه با سیگنال ساعت (همگاه سازی شده یا لبه سیگنال) باشد۰ اگرچه کلمه فلیپفلاپ به شکل کلی به هر دو نوع ساده و همراه با سیگنال ساعت اشاره دارد، اما امروزه، فلیپفلاپ را برای مدارهای دارای سیگنال ساعت استفاده میکنند و برای شکل ساده آن از کلمه لچ استفاده میکنند.

در اصطلاح علمی، لچ حساس به سطح است، و فلیپفلاپ حساس به لبه. به همین دلیل زمانی که لچ فعال میشود، وضعیت آن روشن است در حالی که یک فلیپفلاپ تنها با تغییر حالت ساعت، حالتش تغییر میکند.

تاریخچه

نخستین فیلیپ فلاپها در سال ۱۹۱۸ میلادی توسط ویلیام اکلز و فرانک ویلفرد جوردن اختراع گردید.[1][2]در ابتدا نام آن مدار

تریگر اکلز - جوردن بود و شامل دو عنصر فعال (لامپ خلأ)بود. طراحی آن در سال 1943 در کامپیوتر های کدشکن کلوسوس استفاده شد و این مدار ها و گونه های ترانزیستوری شده آن ها در کامپیوتر ها حتی پس از معرفی مدار مجتمع متداول بودند. با اینکه الان فلیپ فلاپ های ساخته شده از دروازه منطقی متداول هستند, فلیپ فلاپ های اولیه به مدار های تریگر یا مدار نوسانساز معروف بودند.

بنا به پ.ل.لیندلی, مهندسی در آزمایشگاه پیشرانش جت موسوم به جی پی ال, انواع مخلتف فلیپ فلاپ ابتدا در سال 1954 در درس طراحی کامپیوتر دانشگاه کالیفرنیا، لس آنجلس تدریس شده توسط مانتگامری فستر مطرح شدند و سپس در کتاب او طراحی منطقی کامپیوتر های دیجیتال ظاهر شدند. در آن زمان لیندلی در شرکت هواپیماسازی هیوز زیر نظر الدرید نلسون کار می کرد, نلسون اصطلاح جی-کی برای فلیپ فلاپی که وقتی هر دو ورودی آن برابر 1 منطقی هستند تغییر حالت می دهد ابداع کرده بود و بقیه اسم ها توسط فیستر ابداع شده بودند. لیندلی توضیح داده است که داستان فلیپ فلاپ جی-کی را از نلسون که خود مسئول ابداع این اصطلاح است هنگامی که در هواپیماسازی هیوز کار می کرده شنیده است. فلیپ فلاپ هایی که در هیوز استفاده می شدند همه از نوعی بودند که بعدا به فلیپ فلاپ های جی-کی معروف شدند.

انواع فیلیپ فلاپها

فیلیپ فلاپها انواع مختلفی دارند که عبارتند از:[3]

- فلیپ فلاپ SR

- فلیپ فلاپ JK

- فلیپ فلاپ T

- فلیپ فلاپ D

فلیپ فلاپ SR

_Flip-flop.svg.png.webp)

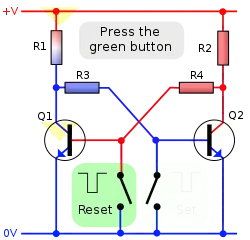

فیلیپ فلاپ SR مداری با دو گیت NAND یا NOR است که بهطور متقاطع به هم وصل گردیدهاند. این مدار دو ورودی Set و Reset دارد. لچ دارای دو حالت مفید است. وقتی خروجی Q=۱ و Q'=۰ لچ در حالت نشانده (منطق۱) است و اگر Q=۰ و Q'=۱ باشد در حالت بازنشانی است. خروجیهای Q و 'Q متمم با این وجود وقتی هر دوی آنها یک شوند حالت تعریف نشده داریم.

| جدول مشخصه فیلیپ فلاپ SR (ساخته شده با گیت NOR([4] | |||||||

|---|---|---|---|---|---|---|---|

| جدول مشخصه | جدول تحریک | ||||||

| S | R | Action | Q(t) | Q(t+1) | S | R | Action |

| ۰ | ۰ | حفظ حالت قبل | 0 | 0 | 0 | X | بدون تغییر |

| 0 | 1 | Q = 0 | 1 | 0 | 0 | 1 | reset |

| 1 | 0 | Q = 1 | 0 | 1 | 1 | 0 | set |

| ۱ | ۱ | حالت تعریف نشده | 1 | 1 | X | 0 | race condition |

X در جدول نشان دهنده حالت بیاهمیت است.

فلیپ فلاپ JK

_Symbol.svg.png.webp)

فلیپ فلاپ JK طبق شکل دارای دو ورودی و دو خروجی و یک پایه کلاک (clk) است. این فیلیپ فلاپ به خاطر پایه کلاک مشکل فیلیپ فلاپ SR را ندارد (در فیلیپ فلاپ SR دو ورودی با هم نمیتوانند یک شوند):

| JK Flip Flop operation[4] | ||||||||

|---|---|---|---|---|---|---|---|---|

| جدول مشخصه | جدول تحریک | |||||||

| J | K | Qnext | Comment | Q | Qnext | J | K | Comment |

| 0 | 0 | Qprev | hold state | 0 | 0 | 0 | X | بدون تغییر |

| 0 | 1 | 0 | reset | 0 | 1 | 1 | X | Set |

| 1 | 0 | 1 | set | 1 | 0 | X | 1 | Reset |

| 1 | 1 | Qprev | toggle | 1 | 1 | X | 0 | No change |

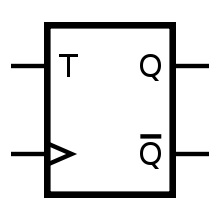

فلیپ فلاپ T

فلیپ فلاپ T فلیپفلاپی است که از آن برای تاگل (Toggle) کردن استفاده میشود. (اگر T=۰ باشد با آمدن کلاک، خروجی همان وضعیت قبلی خواهد بود یعنی اگر صفر باشد خروجی صفر و اگر یک باشد خروجی یک خواهد بود؛ و اگر T=۱ باشد با آمدن کلاک، خروجی معکوس وضعیت قبلی خواهد بود)

| T Flip-Flop operation[4] | ||||||||

|---|---|---|---|---|---|---|---|---|

| جدول مشخصه | جدول تحریک | |||||||

| Comment | Comment | |||||||

| 0 | 0 | 0 | hold state (no clk) | 0 | 0 | 0 | No change | |

| 0 | 1 | 1 | hold state (no clk) | 1 | 1 | 0 | No change | |

| 1 | 0 | 1 | toggle | 0 | 1 | 1 | Complement | |

| 1 | 1 | 0 | toggle | 1 | 0 | 1 | Complement | |

این فلیپ فلاپ به عنوان ذخیرهکننده یک بیت دیتا بسیار پرکاربرد است و از نظر تأخیر نیز شبیه به یک عنصر تأخیر دهنده ساعت عمل میکند به این ترتیب که هر ورودی به آن میدهیم در یک فاصله زمانی مشخصی که به اندازه یک کلاک پالس (پالس ساعت) است همان ورودی را در خروجی دریافت میکنیم. از این رو این فلیپ فلاپ را فلیپ فلاپ تأخیر (Delay) مینامند. این فلیپ فلاپ یک ورودی به نام D دارد. فلیپ فلاپ T همانند فلیپ فلاپ JK است که دو ورودی آن از یک متغیر مقدار میگیرد یعنی یا هر دو J و K مقدار صفر یا هر دو مقدار یک دارند. به این ترتیب در مواقعی یک است، ایجاد جهش میکند.

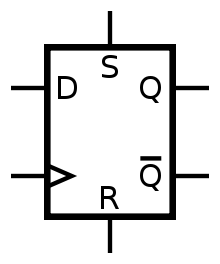

فلیپ فلاپ D

یکی از حالتهای حذف حالت نامطلوب در فلیپفلاپ SR این است که مطمئن شویم هیچگاه آن دو با هم یک نخواهند شد چراکه در فلیپفلاپها ورودی از خروجی قبلی نیز متأثر میشود و وقتی ورودیها هر دو یک باشند پیشبینی خروجی جدید ممکن نیست. این کار با لچ D میسر است زیرا یک ورودی میپذیرد و در ساختار داخلی آن از خود ورودی و عکس (NOT) آن استفاده میشود.

کاربرد

از فلیپفلاپها میتوان در شمارندهها، ذخیرهسازی اطلاعات و … استفاده نمود.

جستارهای وابسته

منابع

- William Henry Eccles and Frank Wilfred Jordan, "Improvements in ionic relays" British patent number: GB 148582 (filed: 21 June 1918; published: 5 August 1920).

- W. H. Eccles and F. W. Jordan (19 September 1919) «A trigger relay utilizing three-electrode thermionic vacuum tubes," The Electrician, vol. 83, page 298. Reprinted in: Radio Review, vol. 1, no. 3, pages 143–146 (December 1919).

- طراحی دیجیتال (مدار منطقی)، پروفسور موریس مانو، ترجمه دکتر قدرت سپیدنام، انتشارات خراسان

- Mano, M. Morris (2004), Logic and Computer Design Fundamentals, 3rd Edition, Kime, Charles R., Upper Saddle River, NJ, USA: Pearson Education International, p. pg283, ISBN 0-13-191165-1

- Digital_logic_circuit_analysis_and_design Nelson

- Fundamental of digital ligic with verilog design by Brown

- Digital_logic_circuit_analysis_and_design by Mano